Toshiba Brings Through-Silicon Vias to NAND Flash

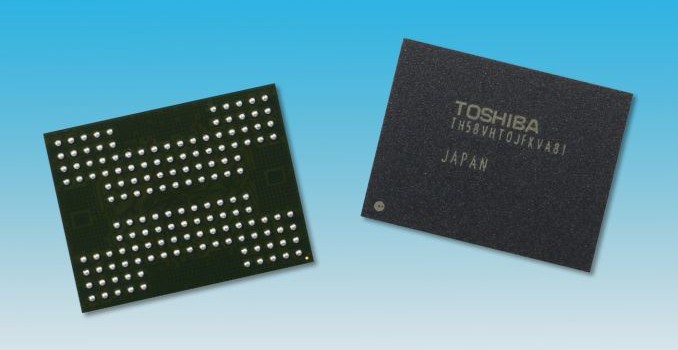

At Flash Memory Summit this week, Toshiba is showing off a NAND flash device packaged using through-silicon vias rather than traditional wire-bonded connections.

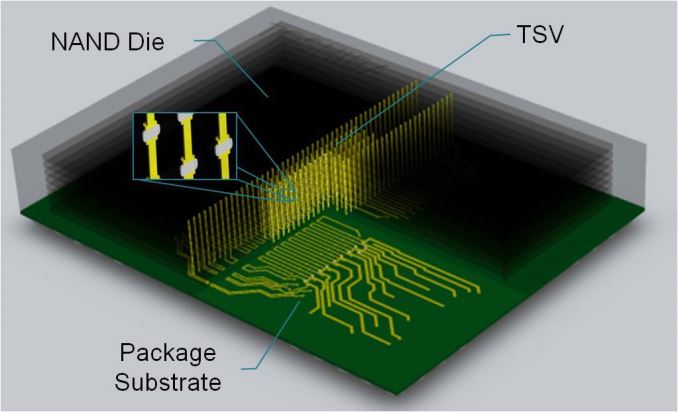

The NAND flash currently on the market is typically produced in the form of a die with a capacity like 128Gb (16GB). The popular SSD form factors don't have enough surface area to fit dozens of those chips, and SSD controllers don't have the pin count to connect to that many independently, so several chips are stacked in a single postage-stamp sized package. The traditional way of connecting the individual dies in a stack is to use the same technique as for a single-die package: bonding a thin gold wire between the edge of the die and the package substrate or external pins. The downsides are that it requires a lot of wires and the edges of the dies in the stack need to be exposed somehow, either by staggering them or by putting a spacer between each layer.

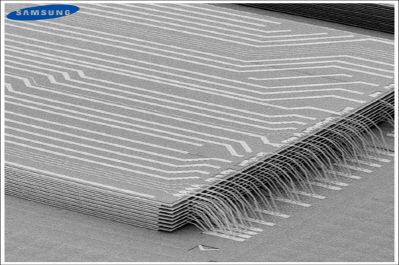

An alternative packaging method is to design the dies to participate in the stacking, by including electrical conductors that penetrate the entire thickness of the silicon die so that they can make contact with the dies above and below it in the stack, essentially tunneling right through each die. These through-silicon vias (TSVs) can then form a shared bus to carry signals from any of the dies in the stack out to the last die, which is the only one with the external connections.

Chip stacking using TSVs requires the dies to be aligned and stacked without spacers, which makes the whole stack a bit more compact. Since TSVs can be placed anywhere on the chip rather than just at the edge, it's easy to implement a wide data bus and communication within the stack can be very fast or low-power due to the short distances involved. These advantages have been very attractive for packaging DRAM, most notably in the form of the HBM stacks used by AMD's R9 Fury and R9 Nano video cards.

Toshiba's demonstration is a 16-high stack of 128Gb dies in a BGA-152 package measuring 14mm by 18mm and 1.9mm thick, and an 8-high stack that's 1.35mm thick. Those numbers are all typical even for wire-bonded stacks. The speed (1Gb/s) and operating voltages (1.2V for I/O and 1.8V core) are what we would expect from a next-generation NAND interface, but the claimed 50% power reduction is a very nice improvement for a change that leaves the flash memory cells themselves unmodified.

Toshiba hasn't said whether the dies being stacked are their current 15nm planar NAND or their forthcoming 3D NAND, nor have they said when modules using TSVs will be hitting the market. The most compelling applications would be to use TSVs to stack flash atop a controller chip in an eMMC product or atop an SoC, but the power savings would be appreciated almost everywhere. If the use of TSVs allows economically stacking more than 16 dies, it could enable a dramatic increase in the density of SSDs.